Micro Magic Inc.—a small electronic design firm in Sunnyvale, California—has produced a prototype CPU that is several times more efficient than world-leading competitors, while retaining reasonable raw performance.

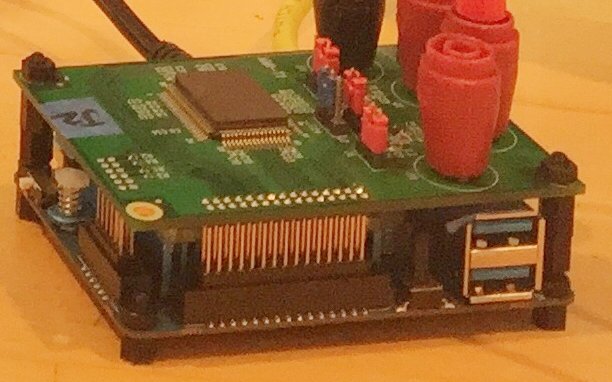

We first noticed Micro Magic’s claims earlier this week, when EE Times reported on the company’s new prototype CPU, which appears to be the fastest RISC-V CPU in the world. Micro Magic adviser Andy Huang claimed the CPU could produce 13,000 CoreMarks (more on that later) at 5GHz and 1.1V while also putting out 11,000 CoreMarks at 4.25GHz—the latter all while consuming only 200mW. Huang demonstrated the CPU—running on an Odroid board—to EE Times at 4.327GHz/0.8V and 5.19GHz/1.1V.

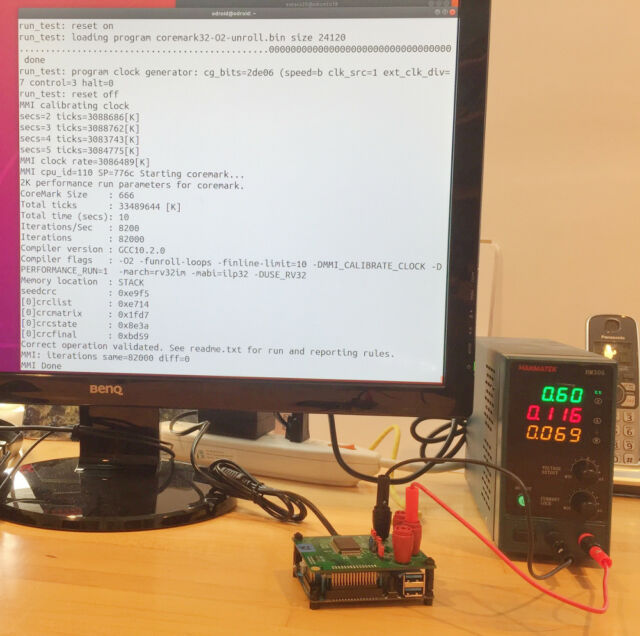

Later the same week, Micro Magic announced the same CPU could produce over 8,000 CoreMarks at 3GHz while consuming only 69mW of power.

OK, but what’s a CoreMark?

Part of the difficulty in evaluating Micro Magic’s claim for its new CPU lies in figuring out just what a CoreMark is and how many of them are needed to make a fast CPU. It’s a deliberately simplified CPU benchmarking tool released by the Embedded Microprocessor Benchmark Consortium, intended to be as platform-neutral and simple to build and use as possible. CoreMark focuses solely on the core pipeline functions of a CPU, including basic read/write, integer, and control operations. This specifically avoids most effects of system differences in memory, I/O, and so forth.

The Embedded Microprocessor Benchmark Consortium (EMBC) is a group with wide industry representation: Intel, Texas Instruments, ARM, Realtek, and Nokia are a few of its more notable and easily recognizable members.

Now that we understood all that, the next step in order to better evaluate Micro Magic’s claims was to run a few CoreMark benchmarks of our own. All we needed to do here was clone its GitHub repository, then issue a make command—optionally, with arguments XCFLAGS="-DMULTITHREAD=8 -DUSE_FORK=1" if we want to test on multiple threads/cores at once.

I still have an Apple M1 Mac Mini on hand, as well as a Ryzen 7 4700U-powered Acer Swift 3, so those were my test systems for comparison. Getting the raw performance scores was considerably easier than getting truly comparable power readings. On the Ryzen-powered Linux system, I used the utility turbostat to get both Core and Package power readings while the tests were running.

I don’t have access to anything nearly as fine-grained as turbostat for the Apple M1, so for that platform I took whole-system power draw at the wall and just plain subtracted the reading at desktop idle from the sustained reading while under test. This is extremely crude, and I caution readers not to rely too much on comparing the M1’s efficiency to the Swift 3’s on these numbers alone—but it’s good enough to get some perspective on Micro Magic’s claim for its new RISC-V (pronounced “risk five”) CPU.

On to the tests!

-

Performance per watt on Micro Magic’s new CPU is eye-popping as compared to typical systems. (It’s worth noting that we had no way to run CoreMark on the M1’s slower, less battery-hungry Icestorm cores only.)Jim Salter

-

Micro Magic’s RISC-V CPU delivers about 1/4 of the raw performance of a single Apple M1 Firestorm core at its hyper-efficient 3GHz clockrate.Jim Salter

-

If you’ve got access to a Linux system, it’s pretty easy to download, compile, and run CoreMark yourself.Jim Salter

The Micro Magic CPU is, for the moment, single-core and single-threaded—although Huang says it could “easily” be built as a 25-core part. Micro Magic has provided figures—and in one case, a screenshot—for performance at 3GHz, 4.25GHz, and 5GHz. At the maximally power-efficient 3GHz clockrate, the Micro Magic CPU scores about one-fourth the CoreMarks of either the Ryzen 4700u or Apple M1. At the maximally performant 5GHz clock, it manages just over a third of their performance.

This is enough to let us know that the Micro Magic chip in its current form isn’t a world-class competitor for traditional ARM and x86 CPUs in phone or laptop applications—but it’s much closer to them than previous RISC-V implementations have been. At the power-efficient 3GHz clockrate, the Micro Magic CPU is nearly three times faster than, for example, SiFive’s Freedom U540 CPU running single-threaded. At 5GHz, it outruns all four of the SiFive’s cores.

At roughly a quarter the performance of world-leading x86 and ARM mobile processors, the Micro Magic CPU doesn’t sound like much yet. But when we factor in power efficiency, things get crazy. I gave my Ryzen and Apple processors the benefit of every possible doubt when generating the above charts—I used core power (not total package power) on the Ryzen 4700U and ran tests with the Gnome3 desktop shut down. For the Apple, I only had access to whole-system power draw, so I subtracted the “desktop idle” power draw from the “under test” power draw.

I tested the Apple and AMD CPUs both single-threaded and multithreaded when checking power efficiency. Unsurprisingly, both parts produced more performance per watt when exercised with one work thread for each available CPU thread. None of this made much of a dent in the Micro Magic’s commanding lead in power efficiency.

At 4.25GHz, the Micro Magic can accomplish the same workload as the Ryzen 4700U with less than one-third the power required. At 3GHz, that figure plummets to less than one-eighth the power required.

What is it good for?

The Linux operating system already supports RISC-V architecture—so for headless or near-headless controllers that simply need to deliver decent performance paired with extreme power efficiency, Micro Magic’s new CPU is likely most of the way there. Things get considerably more complicated once you start talking about entire consumer-friendly systems, of course. Even aside from hardware considerations like GPU and LTE modem, creating an entire Android phone based on a non-ARM architecture is likely to be a much bigger undertaking.

With that said, it’s worth pointing out that—if we take Micro Magic’s numbers for granted—they’re already beating the performance of some solid mobile phone CPUs. Even at its efficiency-first 3GHz clockrate, the Micro Magic CPU outperformed a Qualcomm Snapdragon 820. The Snapdragon 820 isn’t world-class anymore, but it’s no slouch, either—it was the processor in the US version of Samsung’s Galaxy S7.

If we use the EMBC’s published single-core score for the Snapdragon 820 along with Anandtech’s single-core CPU power test result, we get about 16,000 CoreMarks per watt. That’s triple the efficiency of the Ryzen 4700u running single-threaded and a little better than par with it when the Ryzen’s running an optimally multithreaded workload.

In other words, Micro Magic’s prototype CPU is both significantly faster and tremendously more power-efficient than a reasonably modern and still very capable smartphone CPU.

Conclusions

All of this sounds very exciting—Micro Magic’s new prototype is delivering solid smartphone-grade performance at a fraction of the power budget, using an instruction set that Linux already runs natively on. Better yet, the company itself isn’t an unknown.

Micro Magic was originally founded in 1995 and was purchased by Juniper Networks for $260 million. In 2004, it was reborn under its original name by the original founders—Mark Santoro and Lee Tavrow, who originally worked at Sun and led the team that developed the 300MHz SPARC microprocessor.

Micro Magic intends to offer its new RISC-V design to customers using an IP licensing model. The simplicity of the design—RISC-V requires roughly one-tenth the opcodes that modern ARM architecture does—further simplifies manufacturing concerns, since RISC-V CPU designs can be built in shuttle runs, sharing space on a wafer with other designs.

With that said, it would be an enormous undertaking to port—for example—an entire smartphone ecosystem, such as commercial Android, to a new architecture. In addition to building the operating system itself—not just the kernel, but drivers for all hardware from GPU to Wi-Fi to LTE modem, and more—third-party app developers would need to recompile their own applications for the new architecture as well.

We’re also still taking a pretty fair amount of Micro Magic’s claims at face value. While we’ve seen a screenshot of an 8,200 CoreMark score, and we’ve seen a 69mW power reading, it’s not entirely clear that the power reading was representative of the entire benchmark run.

Still, this is an exciting development. Not only does the new design appear to perform well while massively breaking efficiency records, it’s doing so with a far more ideologically open design than its competitors. The RISC-V ISA—unlike x86, ARM, and even MIPS—is open and provided under royalty-free licenses.

https://arstechnica.com/?p=1727410